- 首页

- >

- 学习资源

- >

- 优秀作品

技术征文第5期:时序模块驱动冲突的检查(芯华章篇)--西南交通大学--“无标题”队

2022-07-16 11:09:04

2022-07-16 11:09:04

一、活动背景

集成电路EDA设计精英挑战赛 是国内首个EDA领域专业赛事,赛题覆盖EDA应用及算法,从本科到博士都可参赛,需具备计算机、电子、物理、数学等知识储备,对参赛队伍的要求极具综合性。通过两届大赛的举办,受到了来自产业及高校的高度关注,产业界和学术界专家反馈,参赛作品具有很好的参考和学习价值,继第一届后现选出第二届优秀作品并参与技术征文投稿的队伍作品和大家分享。

二、团队介绍

队伍名称:无标题

队伍成员:刘已秋

所在学校:西南交通大学

获奖情况:2020第二届集成电路EDA设计精英挑战赛全国总决赛一等奖

三、指导老师

邸志雄:西南交通大学信息学院电子系副系主任。主要研究方向为物理实现算法,高性能图像编解码芯片设计。主持国家自然科学基金、四川省科技厅重点项目等,参与完成了我国自主研制的首颗宇航级高速图像压缩芯片“雅芯-天图”(已应用于“嫦娥”系列探月工程等),在IEEE GRSL、IEEE TCAS2、GLS-VLSI、电子学报等发表论文多篇。获2020年“詹天佑-教书育人奖”、2021年阿里云第16期 MVP。

四、赛题介绍

本次分享的作品是由芯华章命制的赛题:时序模块驱动冲突的检查

芯华章:芯华章聚集全球EDA行业精英和尖端科技领域人才,以智能调试、智能编译、智能验证座舱为三大基座,提供全面覆盖数字芯片验证需求的五大产品线,包括:硬件仿真系统、FPGA原型验证系统、智能验证、形式验证以及逻辑仿真,为合作伙伴提供开创性地芯片验证解决方案与专家级顾问服务。同时,芯华章致力于面向未来的EDA 2.0 软件和智能化电子设计平台的研究与开发,以技术革新加速芯片创新效率,让芯片设计更简单、更普惠。

五、作品分享

1、参赛作品背景

在RTL的设计中,时序逻辑的每个输入只能有一个驱动(driver),该驱动可以是组合/时序逻辑的输出。通常,这种错误往往在仿真结果出现问题的时候才能发现,用户调试起来周期非常长,尤其是RTL设计非常大的时候。理想的情况是验证工具进行静态检查(static check),让这类问题在编译阶段(compile time)报出,从而节省用户的调试时间。本赛题就是要求参赛者开发这样一种静态检查的功能。

2、作品成果

在开源RTL仿真工具iverilog的基础上,开发了多驱动检查功能。获赛题一等奖、“芯华章”企业特别奖;该作品为赛题技术测试仅有的两个满分作品之一。

3、作品创新点

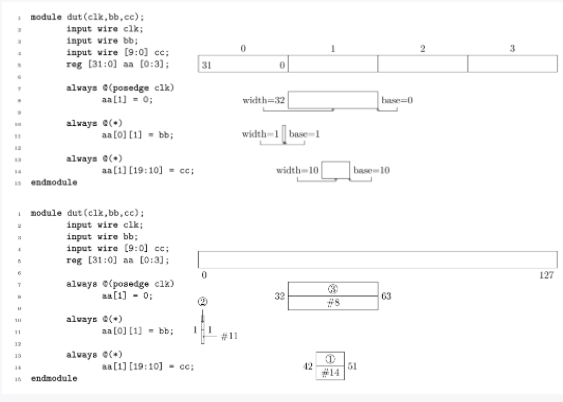

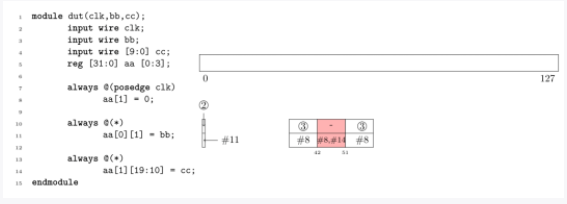

使用整数区间来表示对memory/vector/scalar的复制,这同时稍微简化了问题:

通过整数交集的操作来判断是否存在多驱动:

4、问题及解决思路

1.不熟悉verilog中网表的表示方式,有什么信息、如何获取?

iverilog有对网表信息进行dump的选项。在完成作品过程中,找到了这部分的代码,这部分代码成了每个数据结构的使用示例一样,之后在实现从网表中提取信息的代码的时候,基本都是参照它的访问方式。

2.在for循环的处理中,有碰到需要对表达式进行求值的情况,可能出现的情况比较复杂。

本作品套用了iverilog已有的用于求值常量表达式的函数。对需要求值的数据结构整体进行复制,替换已知量之后调用已有的函数进行求值。

六、团队采访

1、参赛会议

九月报的名,选题主要就是靠兴趣,最后选了时序模块驱动冲突的检查。这个题目要求比较少,只要求verilog语法和C/C++。刚开始的时候,看着代码是有点无从下手的感觉,之后慢慢熟悉题目,熟悉代码之后,搞清概念,有了方案,就实现,慢慢优化,调整。最后,线下很有氛围。

2、指导老师点评

本赛题重点考察学生的C++编程能力,要求学生具有较强的编程基础,熟悉熟悉数据结构。赛题给出了清晰易懂的verilog代码范例,对问题做了聚焦,淡化了集成电路专业背景,因此,赛题面向的学生群范围较广。

本作品参赛选手具有很强的编程能力,对iverilog工具进行了认真分析,设计了较好的数据结构,最终取得了优异的成绩。作品也得到了该赛道命题人的高度评价“我们为赛题开发了随机测试脚本,可以生成几十万行Verilog 代码,一等奖获奖作品通过了我们的严格的压力测试,功能正确(与商用软件结果一致),性能优异”。

本作品为大四本科生刘已秋同学一人独立完成,在比赛中,与硕士、博士同场竞技,成绩来之不易,也充分证明了该同学扎实的编程能力。