- 首页

- >

- 学习资源

- >

- 优秀作品

技术征文第6期:时序模块驱动冲突的检查(芯华章篇)--西安电子科技大学-“没有人比我更懂EDA”队

2022-07-16 11:08:22

2022-07-16 11:08:22

一、活动背景

集成电路EDA设计精英挑战赛 是国内首个EDA领域专业赛事,赛题覆盖EDA应用及算法,从本科到博士都可参赛,需具备计算机、电子、物理、数学等知识储备,对参赛队伍的要求极具综合性。通过两届大赛的举办,受到了来自产业及高校的高度关注,产业界和学术界专家反馈,参赛作品具有很好的参考和学习价值,继第一届后现选出第二届优秀作品并参与技术征文投稿的队伍作品和大家分享。

二、团队介绍

队伍名称:没有人比我更懂EDA

队伍成员:郭广鑫 陈灿 袁朗

所在学校:西安电子科技大学

获奖情况:2020第二届集成电路EDA设计精英挑战赛全国总决赛菁英杯

三、指导老师

游海龙,西安电子科技大学微电子教授,博士;美国佐治亚理工学院(Georgia institute of technology)博士后;兼聘西电管理科学与工程学科研究生导师,西电-国微EDA研究院副院长,西安市系统芯片与微系统重点实验室副主任。主要研究方向为集成电路可靠性与设计自动化,长期从事半导体制造过程控制、集成电路设计自动化与可靠性设计等关键技术研究。

祁仲冬,西安电子科技大学准聘副教授,博士;长期研究电子设计自动化中的算法设计与建模问题,以及人工智能应用。已在国际学术会议和期刊上发表论文10篇,其中包括中国计算机学会(CCF)列表A类论文1篇,B类论文2篇,C类论文2篇,并获得CCF B类会议ICCD 2014最佳论文提名。

四、赛题介绍

本次分享的作品是由芯华章命制的赛题:时序模块驱动冲突的检查

芯华章:芯华章聚集全球EDA行业精英和尖端科技领域人才,以智能调试、智能编译、智能验证座舱为三大基座,提供全面覆盖数字芯片验证需求的五大产品线,包括:硬件仿真系统、FPGA原型验证系统、智能验证、形式验证以及逻辑仿真,为合作伙伴提供开创性地芯片验证解决方案与专家级顾问服务。同时,芯华章致力于面向未来的EDA 2.0 软件和智能化电子设计平台的研究与开发,以技术革新加速芯片创新效率,让芯片设计更简单、更普惠。

五、作品分享

1、题目要求

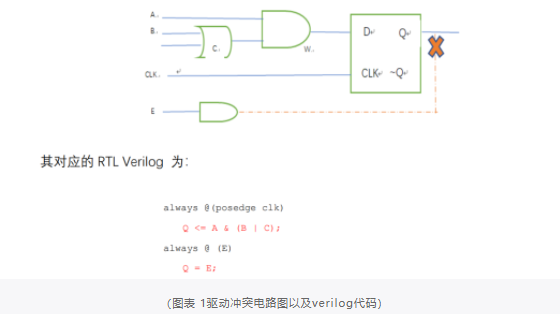

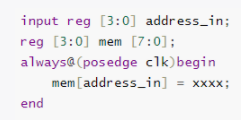

在实际 RTL 开发中,有一类比较常见的错误,就是一个时序电路的输出(如 Q)会有多个 驱动,如:

通常,这种错误往往在仿真结果出现问题的时候才能发现, 用户调试起来周期非常长,尤其是 RTL 设计非常大的时候。理想的情况是验证工具进行静态检查(static check),让这类问题在编译阶段(compile time)报出,从而节省用户的调试时间。本赛题就是需要开发这样一种静态检查的功能。

2、问题分析

我们需要了解在RTL级Verilog代码中可能造成驱动冲突的各种赋值类型:首先,总的分为always块和initial块,因为initial之间不会产生冲突,所以所有的initial的块可以整合为一个always块,相同always块对同一寄存器赋值不会产生驱动冲突,而不同always块对同一寄存器赋值会产生驱动冲突;另外,需要支持 scalar type 类型,vector/memory 类型以及位选和片选。支持嵌套的 forloop 分析,同时还有for 条件中带有变量值的非常规 verilog 赋值方式。支持层级引用(hierachical reference)、case 和 if else 语句、task 语句、repeat 语句和延时语句。

3、参考资料分析

1)基于开源项目iverilog:从iverilog官方开发手册入手,着重了解:a. iverilog的实现过程b. 思考具体应该在什么地方加入驱动冲突检测的概念。

2)读源代码:将verilog中的变量和语法结构和iverilog中的数据结构一一对应。熟悉原作者的编程风格。熟悉verilog在iverilog工程中已经实现的数据结构的功能,方便调用。

3)Verilog标准:IEEE_Std 1364-2005,例如寄存器片选索引规则之类。

4、实现思路

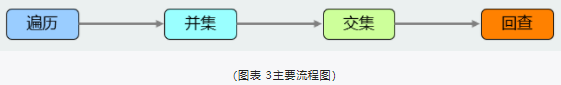

经过上面的分析,已经可以对已有的内容有了整体的了解,基于已知内容,就可以着手实现的过程。主要过程分为4步,如图表 3所示:

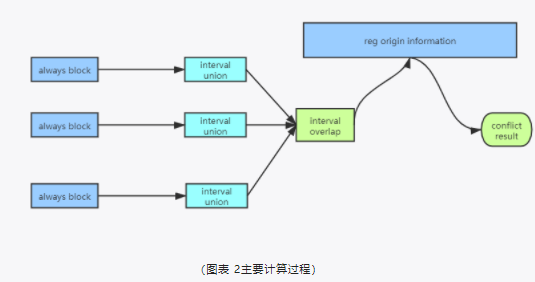

参照图表2,首先,遍历所有赋值语句,存被驱动变量到原始hash表中。接着,同一个always block中相同变量的区间求并集。然后,不同block中相同变量的区间求交集,计算冲突的具体位数。最后,根据冲突结果去原始节点hash表寻找区间被赋值的位置信息。

5、问题及解决思路

1) 如何高效存储被驱动的寄存器?

在verilog中存在着大量的多bit寄存器,所以为了减少存储量和计算任务,只保留被驱动的最高位和最低位,代表被驱动区间,使用变量的索引区间来确定驱动范围,大大提高了性能。

2) 如何高效计算循环语句中可能被驱动的bit位?

verilog不是一种展平的硬件描述,所以存在很多类似于for等循环语句。例如,为了快速判断寄存器的哪些bit被赋值,要对for扩展循环语句快速展开。循环中可能会产生大量赋值的过程,通过分析for语句的初始条件、终止条件和变量增加条件,快速判断出信号的哪些位会被赋值,这样就不用对for进行展开运算,大大提高了速度。

3) 如何减少对于未知可能潜在的冲突的计算量?

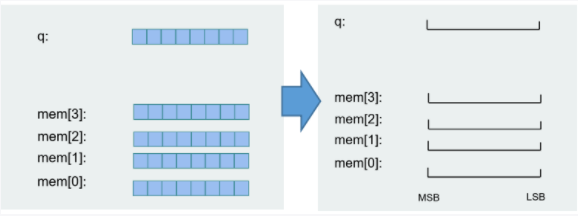

为了保证所有的驱动冲突都可以被检测到,对于位宽很大的二维寄存器(memory)有可能需要存储和计算很多的计算量。如下图所示:

针对这种情况,我们用特殊值,只需要一个字就可以替代所有的潜在冲突,计算量骤减,所以很大地提高了速度。

六、团队采访

1、如何选择赛题

充分了解各个赛题。只有充分了解,才能全面把握赛题。适合自己。有专业优势,并且感兴趣的赛题。符合导师方向。老师学长会给予很多帮住。确定赛题后,仔细研读赛题,对相关的研究进行调查。对赛题任务进行划分,队伍各个分工明确,各司其职。制定时间节点,按计划完成任务。

2、指导老师采访

该作品的功能覆盖率很高,运行速度很快, 能够完成很具有压力的测试,同时代码的模块化设计使得其逻辑清晰,层级关系明显,注释完备, 对日后的维护也十分便利。对该题有兴趣的话,推荐的资源有芯华章开源仿真器:https://github.com/x-epic.EpicSim以及编译原理(龙书)。

3、大赛记忆

本次的eda挑战赛给我们留下了宝贵的记忆。不仅仅是最后获得了大奖菁英杯的那一刻,这一路的努力和坚持同样让人收获颇丰,记忆犹新。很感谢大赛方能够提供这样一个机会能让全国热爱eda的人互相交流,同台竞技。这次比赛首先锻炼了我们的编程能力。

从读开发者手册到读源代码,到最后的代码实现,我们的编程技能有了很大的提升。这离不开赛方的热心回答和老师的指导。其次,培养了我们解决困难的能力。遇到困难后,不要轻易放弃,总归是能解决的。最后,给了我们继续前行的信心,这次的获奖无疑是对我们工作和方向的肯定,这让我们更能够将全身心投入到研发国产eda软件中去。